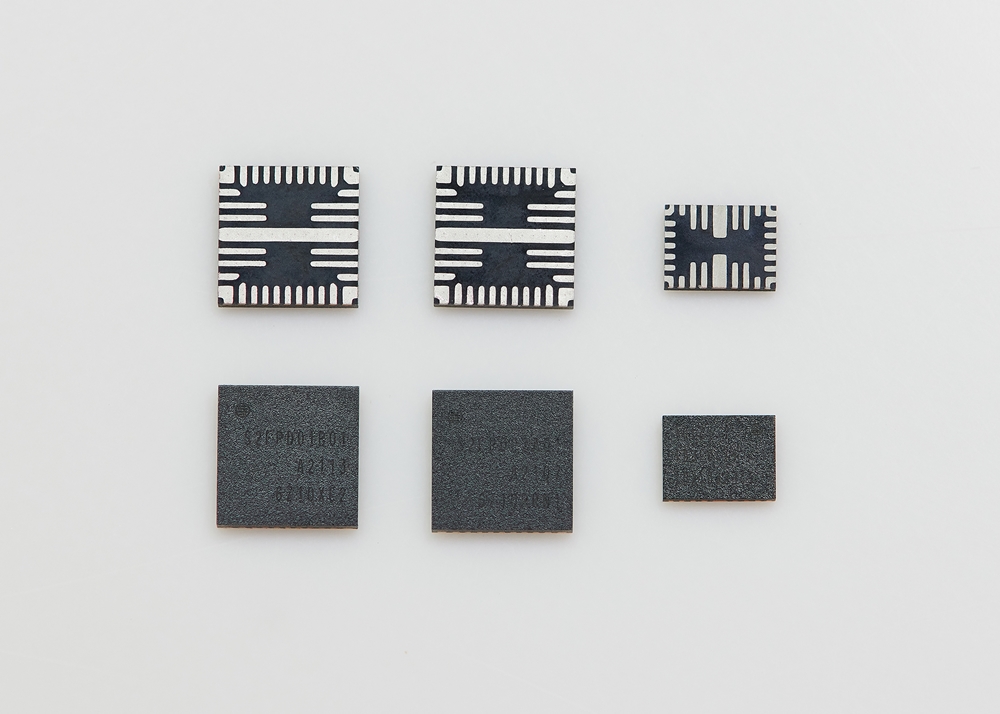

삼성전자, 업계 최선단 14나노 EUV DDR5 D램 양산

삼성전자 가 EUV(극자외선, Extreme Ultra-Violet) 공정을 적용한 업계 최선단 14나노 D램 양산에 들어갔다. 삼성전자는 2020년 3월 업계 최초로 EUV 공정을 적용한 D램 모듈을 고객사들에게 공급한 바 있으며, 업계에서 유일하게 EUV 멀티레이어 공정을 적용해 최선단 14나노 D램을 구현하는 등 차별화된 공정 기술력을 선보이고 있다. 삼성전자는 반도체 회로를 보다 세밀하게 구현할 수 있는 EUV 노광 기술을 적용해 D램의 성능과 수율을 향상시켜, 14나노 이하 D램 미세 공정 경쟁에서 확고한 우위를 확보해 나갈 계획이다. 5개의 레이어에 EUV 공정이 적용된 삼성전자 14나노 D램은 업계 최고의 웨이퍼 집적도로 이전 세대 대비 생산성이 약 20% 향상됐다. 또한, 삼성전자 14나노 D램 제품의 소비전력은 이전 공정 대비 약 20% 개선됐다. 삼성전자는 이번 신규 공정을 최신 DDR5(Double Data Rate 5) D램에 가장 먼저 적용한다. DDR5는 최고 7.2Gbps의 속도로 DDR4 대비 속도가 2배 이상 빠른 차세대 D램 규격으로 최근 인공지능, 머신러닝 등 데이터를 이용하는 방식이 고도화 되면서 데이터센터, 슈퍼컴퓨터, 기업용 서버 시장 등에서 고성능 DDR5에 대한 수요가 지속 커지고 있다. 삼성전자는 업계 최선단의 14나노 공정과 높은 성숙도의 EUV 공정기술력을 기반으로 차별화된 성능과 안정된 수율을 구현해, DDR5 D램 대중화를 선도한다는 전략이다. 또한 삼성전자는 고용량 데이터 시장 수요에 적극 대응하기 위해 이번 공정으로 단일 칩 최대 용량인 24Gb D램까지 양산할 계획이다. 삼성전자 메모리사업부 D램개발실장 이주영 전무는 “삼성전자는 지난 30년간 끊임없는 기술 혁신을 통해, 반도체 미세 공정의 한계를 극복해 왔으며, 이번에도 가장 먼저 멀티레이어에 EUV 공정을 적용해 업계 최선단의 14나노 공정을 구현했다”며, “고용량, 고성능 뿐만 아니라 높은 생산성으로 5G·AI·메타버스 등 빅데이터 시대에 필요한 ...